| Предыдущий раздел | ВЫПОЛНЕНИЕ ПРОГРАММ ПРОЦЕССОРОМ I8086 | Следующий раздел |

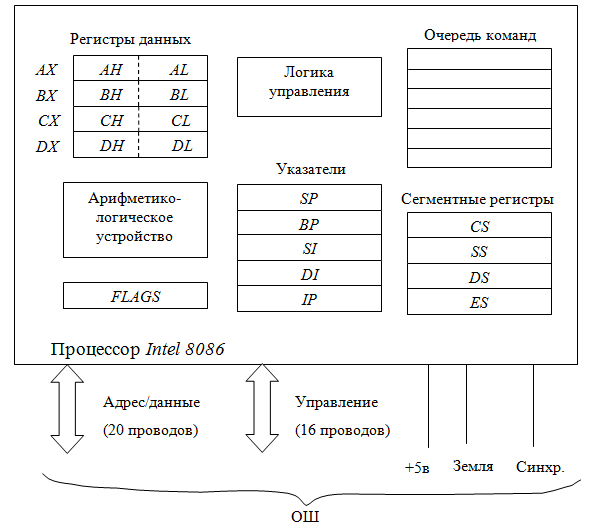

На рис. 7 приведена архитектура (структура) микропроцессора i8086. Рассмотрим назначение его основных модулей.

Рис. 7. Структура микропроцессора i8086

Блок логика управления выполняет дешифрирование и исполнение машинных команд. Если очередная команда является арифметической или логической, то она направляется логикой управления для выполнения в арифметико-логическое устройство.

Регистры данных предназначены для хранения операндов и результатов операций. Регистр – ячейка памяти, скорость обмена с которой намного выше, чем с другими видами памяти: с ОП и, тем более, с ВП. К регистрам данных относятся регистры АХ, ВХ, СХ и DX. Они допускают адресацию не только целых регистров, но и их младшей и старшей половин. Например, допускается использовать два байта в регистре АХ вместе, а также указывать отдельные байты - AL (младший) и АН (старший). Регистры ВХ, СХ и DX, кроме обычных функций, имеют и специальные назначения.

Очередь команд содержит текущую команду на время ее дешифрации (распознавания) и выполнения. Кроме того, для повышения быстродействия в данную очередь заранее считываются из ОП следующие по порядку в программе команды. Длина очереди команд – 6 байт.

В группу регистров указатели входят указатель команды IP и указатель стека SP, а также регистры ВР, SI и DI. Указатель команды IP – очень важный регистр, который содержит относительный адрес (смещение) следующей команды, подлежащей выполнению на ЦП. Указатель стека SP также очень важен: он содержит относительный адрес вершины стека. Подробнее регистры IP и SP будут рассмотрены позже.

Остальные регистры-указатели используются для адресации ячеек какого-то массива относительно его начала. При этом базовый регистр ВР часто используется для адресации ячеек программного стека относительно его вершины. А индексные регистры SI и DI обычно используются при циклической обработке элементов массива. При этом для того, чтобы обрабатывать одной и той же машинной командой различные ячейки массива, достаточно перед выполнением тела цикла осуществлять изменение содержимого того индексного регистра, который используется для адресации ячеек массива.

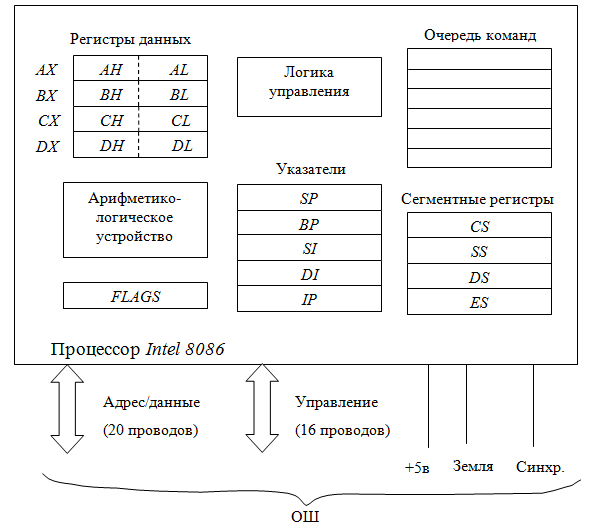

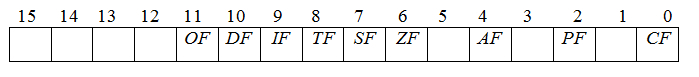

Регистр флагов FLAGS отражает текущее состояние ЦП. Структура этого регистра приведена на рис. 8.

Рис. 8. Регистр флагов микропроцессора i8086

Cемь битов в FLAGS не используются. Остальные биты (флажки) делятся на условные и управляющие. Условные флажки отражают результат предыдущей арифметической или логической операции. Это:

1) SF – флаг знака. Равен старшему биту результата. Так как в дополнительном коде старший бит отрицательных чисел содержит 1, а у положительных он равен 0, то SF показывает знак предыдущего результата;

2) ZF – флаг нуля. Устанавливается в 1 при получении нулевого результата и сбрасывается в 0, если результат не равен 0;

3) PF – флаг паритета. Устанавливается в 1, если младшие 8 битов результата содержат четное число единиц, в противном случае он сбрасывается в 0;

4) CF – флаг переноса. При сложении (вычитании) устанавливается в 1, если возникает перенос (заем) в старший бит (из старшего бита). Обычно данный флаг используется не по прямому назначению, а как признак возврата из подпрограммы: если подпрограмма (процедура или обработчик прерываний) завершилась успешно, то она возвращает CF=0, а если с ошибкой, то CF=1;

5) AF – флаг вспомогательного переноса. Устанавливается в 1, если при сложении (вычитании) возникает перенос (заем) из бита 3. Флаг предназначен только для двоично-десятичной арифметики;

6) OF – флаг переполнения. Устанавливается в 1, если знаковый бит изменился в той ситуации, когда этого не должно было произойти.

Пусть, например, машинная команда add (здесь и везде далее используются ассемблерные мнемоники машинных команд) выполнила следующее сложение:

0010 0011 0100 0101

+ 0011 0010 0001 1001

0101 0101 0101 1110 ,

тогда после ее выполнения получаются состояния флажков:

SF = 0, ZF = 0, PF = 0, CF = 0, AF = 0, OF = 0 .

Если add выполнила сложение:

0101 0100 0011 1001

+ 0100 0101 0110 1010

1001 1001 1010 0011 ,

то флажки принимают состояния:

SF = 1, ZF = 0, PF = 1, CF = 0, AF = 1, OF = 1 .

Флажки управления влияют на выполнение специальных функций. Эти флажки устанавливаются лишь несколькими специальными машинными командами. Это флажки:

1) DF – флаг направления. Он используется при выполнении команд, обрабатывающих цепочки – последовательности ячеек памяти. Если флаг сброшен, цепочка обрабатывается с первого элемента, имеющего наименьший адрес. Иначе цепочка обрабатывается от наибольшего адреса к наименьшему;

2) IF – флаг разрешения прерываний. Когда установлен этот флажок, ЦП выполняет маскируемые прерывания. Иначе эти прерывания игнорируются;

3) TF – флаг трассировки. Если этот флажок установлен, то после выполнения каждой машинной команды, ЦП генерирует внутреннее аппаратное прерывание (прерывание номер 1).

Рассмотренный регистр FLAGS чрезвычайно важен не только для понимания логики работы ЦП, но и всей ЭВМ в целом. Это обусловлено тем, что данный регистр фактически является дескриптором ЦП. Дескриптор (или блок управления) – структура данных, используемая для управления модулем ЭВМ. При этом каждый сколько-нибудь сложный модуль ВС имеет свой блок управления.

Последний блок ЦП образуют сегментные регистры CS, SS, DS и ES. Данные регистры используются для адресации ячеек ОП.

| Предыдущий раздел | В начало | Следующий раздел |